DNN 加速器

DNN加速器综述

硬件方案

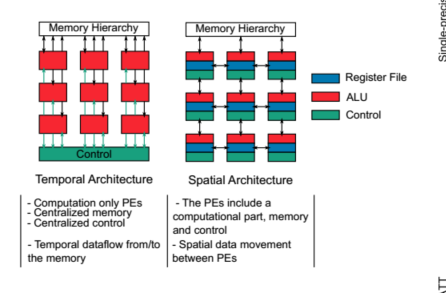

两种架构:temporal and spatial architectures

其中asic和fpga主要为spatial结构,而CPU和GPU主要为temporal结构

本次主要介绍空间架构

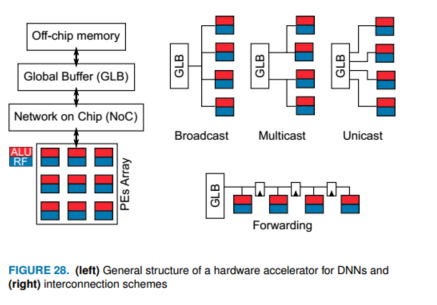

这种结构有相当一部分能耗在存储上,故数据重用是研究重点

一些重用名词

input reuse:FC层

weight reuse:CONV层

conv reuse:卷积层的滑窗每次都有重复的

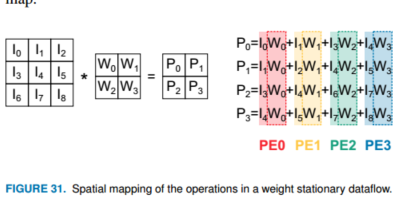

Weight Stationary

所有使用相同weight的mac必须映射到同一PE上进行串行处理。这最大限度地提高了RF中权重的卷积和滤波器重用,从而最大限度地减少了访问权重的能量消耗

这是一个3x3的矩阵2x2的卷积核,最后生成2x2的输出

先说上面那一种

仅介绍一个输出元素如何产生的,

T1:I0XW0

T2:I0XW0+I1XW1

T3:将结果移入PE2

T4:I0XW0+I1XW1+I2XW2

T5:I0XW0+I1XW1+I2XW2+I3XW3,完成一次卷积操作

下面哪一种和上面类似,不过是再次分块了

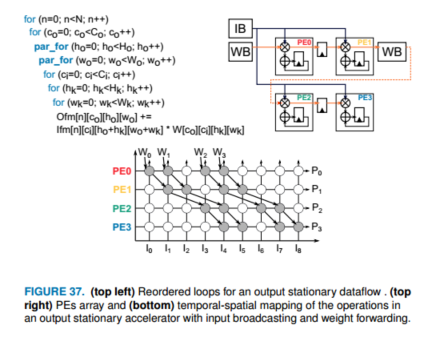

Output Stationary

映射规则是对相同的输出像素的所有mac必须依次映射到同一PE上。

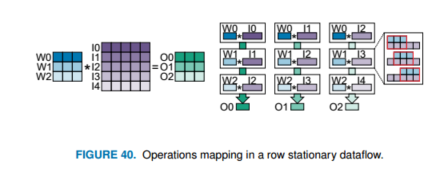

Row Stationary

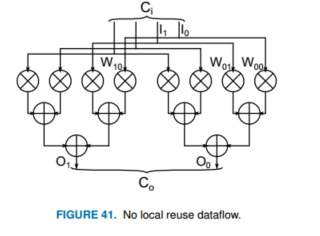

No Local Reuse